|

|

МЕНЮФестивали и конкурсы Семинары Издания О МОДНТ Приглашения Поздравляем НАУЧНЫЕ РАБОТЫ |

Реферат: Методы размещения и трассировки печатных плат на примере модуля памятиРеферат: Методы размещения и трассировки печатных плат на примере модуля памятиСодержание ВВЕДЕНИЕ................................................................................................................ 2 1. ВЫБОР СЕРИИ И ТИПОВ МИКРОСХЕМ И РАСПРЕДЕЛЕНИЕ ЭЛЕМЕНТОВ ФУНКЦИОНАЛЬНОЙ СХЕМЫ ПО КОРПУСАМ............................................. 3 1.1. Выбор физических элементов для реализации схемы и обзор параметров выбранной серии..................................................................................................... 3 1.2. Распределение элементов функциональной схемы по корпусам............ 4 2. РАЗМЕЩЕНИЕ ЭРЭ НА МОНТАЖНОМ ПРОСТРАНСТВЕ..................... 6 3. ТРАССИРОВКА МОНТАЖНЫХ СОЕДИНЕНИЙ...................................... 10 3.1 Трассировка с помощью алгоритма Прима............................................... 10 3.2 Трассировка по алгоритму Краскала.......................................................... 12 3.3 Трассировка классическим волновым алгоритмом Ли............................ 14 ЗАКЛЮЧЕНИЕ....................................................................................................... 15 ЛИТЕРАТУРА......................................................................................................... 16 Основные принципы изготовления и применения печатных схем стали известны в начале ХХ века, однако промышленный выпуск печатных схем и плат был организован лишь в начале 40-х годов. С переходом на микроэлектронные элементы, резким уменьшением размеров и возрастанием быстродействия схем первое место занимают вопросы обеспечения постоянства характеристик печатных проводников и взаимного их расположения. Значительно усложнились задачи проектирования и оптимального конструирования печатных плат и элементов. Печатные платы нашли широкое применение в электронике, позволяя увеличить надёжность элементов, узлов и машин в целом, технологичность (за счёт автоматизации некоторых процессов сборки и монтажа), плотность размещения элементов (за счёт уменьшения габаритных размеров и массы), быстродействие, помехозащищённость элементов и схем. Печатный монтаж – основа решения проблемы компановки микроэлектронных элементов. Особую роль печатные платы играют в цифровой микроэлектронике. В наиболее развитой форме (многослойный печатный монтаж) он удовлетворяет требования конструирования вычеслительных машин третьего и последующих поколений. При разработке конструкции печатных плат проектеровщику приходится решать схемотехнические (минимизация кол-ва слоёв, трассировка), радиотехнические (расчёт паразитных наводок), теплотехнические (температурный режим работы платы и элементов), конструктивные (размещения), технологические (выбор метода изготовления) задачи. В данном курсовом проекте при разработке печатной платы мы попытались показать методы решения лишь схемотехнических и технологических задач. 1. ВЫБОР СЕРИИ И ТИПОВ МИКРОСХЕМ И РАСПРЕДЕЛЕНИЕ ЭЛЕМЕНТОВ ФУНКЦИОНАЛЬНОЙ СХЕМЫ ПО КОРПУСАМ. 1.1. Выбор физических элементов для реализации схемы и обзор параметров выбранной серии. Выбор серии интегральных микросхем для реализации блока оперативной памяти в первую очередь продиктован скоростью работы такого блока. В этом отношении микросхемы серии ТТЛШ (транзисторно–транзисторная логика со структурой Шотки) наиболее предпочтительны. Электрическая функциональная схема блока оперативной памяти содержит сорок пять элементов 2И-НЕ, три элемента 3И-НЕ. Для реализации блока оперативной памяти выбираем следующие типы

микросхемы: Основные параметры микросхем ТТЛШ серии КР1531: 1.2. Распределение элементов функциональной схемы по корпусам. Распределение четырёх элементов 2И-НЕ составляющих триггер очевидно:

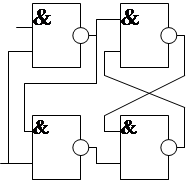

Поскольку внутренних связей в таком элементе гораздо больше чем внешних, то очевидно их помещение в одну микросхему КР1531ЛА3. Для распределения девяти оставшихся элементов 2И-НЕ по трём корпусам микросхем КР1531ЛА3 вычерчиваем часть электрической функциональной схемы блока оперативной памяти, содержащую эти элементы, и строим соответствующий ей граф G1 (рис.1.1).

Рис. 1.1 а) Выбираем базовую вершину – вершину имеющую максимальное количество связей. Поскольку в нашем случае все вершины имеют одинаковое количество связей, выбираем любую из них, например вершину Х1. б) Определяем множество вершин подключённых к базовой: {4;7} Li=aij-pij где aij – число

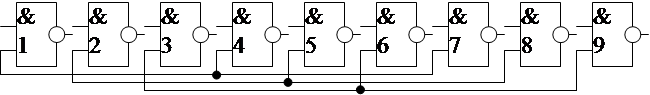

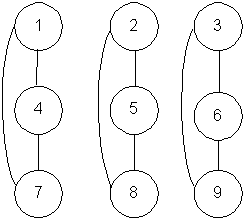

связей вершины; В нашем случае функционал равен: L7=L4=2-1=1; Для объединения с базовой вершиной необходимо выбрать вершину с наименьшим функционалом. Поскольку в нашем случае вершины Х7 и Х4 равнозначны, то объединяем их с Х1. Поскольку мощность блока (4 элемента 2И-НЕ в одной микросхеме) ещё не достигнута, а все оставшиеся вершины идентичны по отношению к вершине Х(1+4+7), дополним блок вершиной Х2, объединив их в одну микросхему. Получим граф:

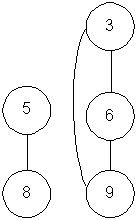

Теперь, в качестве базовой изберём вершину Х3. Рассуждая так же как и в предыдущем шаге объединим в одну микросхему вершины Х3, Х6, Х9 и Х5. Вершину Х8 придётся поместить в отдельную микросхему. Проанализировав полученные результаты можно увидеть, что для компоновки элементов Х1-Х9 необходимо 3 микросхемы КР1531ЛА3, причём в последней из них будет задействован лишь один элемент. В нашем случае рациональней будет уменьшить мощность блока до трёх. В этом случае количество необходимых микросхем не изменится, а элементы распределятся следующим образом: Х(1+4+7), Х(2+5+8), Х(3+6+9). Окончательно примем к проектированию именно такой вариант компоновки. Три элемента 3И-НЕ поместим в одну микросхему КР1531ЛА3 поскольку в этом случае мощность блока (кол-во элементов в микросхеме) равна количеству элементов в функциональной схеме. На основании полученных результатов строим электрическую принципиальную схему блока оперативной памяти (см. графическую часть). 2. РАЗМЕЩЕНИЕ ЭРЭ НА МОНТАЖНОМ ПРОСТРАНСТВЕ. В соответствии с заданием монтажное пространство — печатная плата 95х130 мм. Для размещения микросхем DD1—DD13 и разъема Х1 разобьем монтажное пространство на 14 посадочных мест, из которых место К14 отведем под разъем (рис.2.1).

Рис. 2.1 Составим матрицу расстояний для приведённой платы:

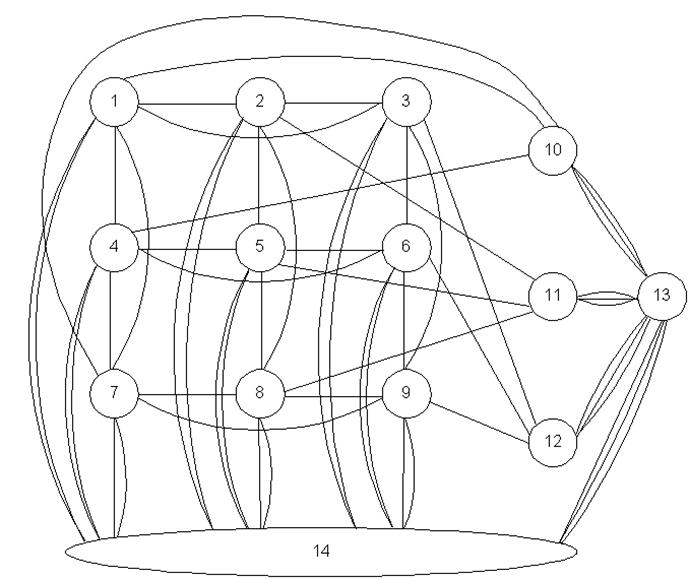

Приведём полный граф электрической принципиальной схемы (рис. 2.2). Элементы 1…12 – микросхемы КР1531ЛА3, элемент 13 – микросхема КР1531ЛА4, а элемент 14 – разъём.

Матрица смежности этого графа имеет вид:

Для размещения корпусов микросхем на печатной плате воспользуемся последовательным алгоритмом размещения: |

Приглашения09.12.2013 - 16.12.2013 Международный конкурс хореографического искусства в рамках Международного фестиваля искусств «РОЖДЕСТВЕНСКАЯ АНДОРРА»09.12.2013 - 16.12.2013 Международный конкурс хорового искусства в АНДОРРЕ «РОЖДЕСТВЕНСКАЯ АНДОРРА»

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Copyright © 2012 г.

При использовании материалов - ссылка на сайт обязательна.